100億トランジスタのチップを

確実に設計する高信頼技術

電子・電気材料工学、電子デバイス・電子機器

デジタル回路、アナログ回路、アナログ/デジタル混載回路、ロジックLSI、メモリLSI、通信用LSI、高速インターフェース、 LSI設計CAD、シグナル・インテグリティ

21世紀を迎えた今日、我々の日常生活において、コンピュータやインターネット、携帯電話などに代表されるIT技術は、もはや必要不可欠なものとなっています。これらの技術の進展を根底から支えてきたものの一つが大規模集積回路(VLSI)技術です。これまでは主として、CMOS素子の微細化による製造技術の改善によりLSIの性能向上が図られてきましたが、もはや物理限界といわれるサブミクロン(0.1μ-6m)時代を直前に迎え、現在では、回路設計技術やチップアーキテクチャにおける新しいアイデア創出によるブレークスルーへの期待が高まっています。本研究は、高速化・低電力化・高集積化といったLSIの高性能化の基本課題に対して、新規な回路・アーキテクチャを提案し、回路シミュレーションによる検討や、実際にLSIを試作・評価することで、その効果を検証するものです。一方で、高性能な大規模LSI回路を効率的に設計するための設計手法についても、特に性能の差別化に大きく貢献する回路をレイアウトレベルから検討を行い、次世代の超大規模LSIのあるべき姿について探求しています。

全体の研究概要(サブテーマ全体像)は、図表・写真を参照

研究サブテーマ

① グローバル経年素子劣化回路シミュレータの開発

② フレキシブルアナログIPの設計・開発(電圧安定化回路への適応)

③ Static Noise Margin (SNM) を用いた高動作マージン設計法

~ 発振回路への適用 ~

微細化の進展によって、近年とくに素子ばらつきの影響や、素子性能の経年劣化が大きな問題になってきました。素子ばらつきや経年劣化の状況をシミュレーションするシステムの開発、それらの悪影響を回避する回路設計技術について今後研究を進めていきます。さらには、半導体LSI技術をベースとし省エネルギーやロボット・バイオテクノロジーなど、新規応用分野への展開を探索します。

① 『LSIテスター装置』 試作したLSIの動作確認を行い、その性能を定量的に評価する

② 『LSI信頼性評価装置』 LSIを高温下のストレス状態で動作させる

▶『SRAMメモリセルの評価方法及びSRAMメモリセルの評価プログラムをコンピュータが読み取り可能に記録した記録媒体』、特願2007-095928

▶『電子回路デバイス』、特願2007-089951(製造後補正可能な3端子レギュレータ回路)

北九州ヒューマンテクノクラスター(知的クラスター:第1期)の研究テーマとして、大学において研究を進めていました、PermSRAM技術(標準的なCMOSプロセス工程のみで実現できる新規不揮発メモリ)の基本技術開発に2004年度に成功しました。本成果を事業化するために、大手半導体メーカーから人材を集め、北九州市と産総研のベンチャー支援制度の支援を受け、2005年3月に(株)NS Core(本社:北九州市)を設立しました。NS Core社へ本技術の基本特許を譲渡するとともに、自らも研究技術担当として取締役を兼業し、2005年には、民間のベンチャーキャピタルから計1.3億円の出資を受けることに成功しました。その後、福岡県やJSTからの研究開発補助金(計約1.2億円)の獲得に成功し、製品化を推進、2006年に最初に譲渡したPermSRAM技術の基本特許が米国において成立(US-7151706)したことから、ベンチャーのビジネスモデルとして確立し、2007年には、国内大手半導体メーカーと1億円以上のライセンス契約を結ぶまでになりました。2009年度末の株式公開を目標としており、現在、資本金2.3億円、従業員15名まで成長しています。

サブテーマ①

未来予測経年素子劣化10年後、20年後の性能を予測する回路シミュレータ

回路設計・経年変化・温度変動等のデータを「グローバル経年変化回路シミュレータ」に通すことにより、10年後、20年後の劣化が予測できます。

・時間加速によりに回路各素子(MOSFET)の動作状況に対応する劣化状況を逐次計算 ・HCI、NBTI、TDDBなどの経年劣化モデル+動的温度変動に対応 ・地球上の任意の場所での任意の時間経過後の回路動作を動作波形として検証可能 ・各回路素子毎の劣化状態を算出可能⇒素子劣化に耐性を持つ回路の検討が可能に! ・商用SPICEとの互換化により、既存の設計フローへシームレスに結合

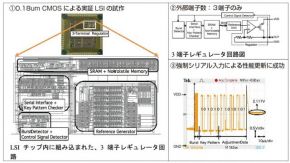

サブテーマ②

製造後性能補正が可能な3端子レギュレータ

背景とメリット:3端子レギュレータ、3端子の水晶発振器などのパッケージ実装後における特性変更の可否についてニーズがあり、その実現可能性の検討から始まった研究です。小端子数デバイスの特性/精度の向上、調整あるいは管理コストの削減において有用と考えられる技術です。

<新技術の特徴・従来技術との比較>

・ 組み立て後、3端子レギュレータの出力電圧を信号入力により変更可能とすることに成功

・ 他の諸特性も調整可能で、より高精度かつ高性能の3端子レギュレータが実現可能

・ 本技術の適用により、調整用の外付け部品なしで特性変更が可能となるため実装面積、調整コストなどが削減される事が期待

・ 従来に比べ高速であり、ノイズおよび誤信号に強い1線シリアル・インターフェースを構築可能

・ インターフェース回路設計は比較的容易であり、面積及び消費電力の増大も小さい

・ 本技術の適用により、端子数増加を最小限に抑えた設定可能デバイスの実現が可能

<従来技術とその問題点>

すでに実用化されている1線シリアルI/Fには、マキシム社から提唱されているプロトコルがあります。1ビットの通信に60µs以上かかる通信速度は低く、低域の高強度ノイズやデバイスON時の不整信号に誤反応する可能性があり、信頼性に不安が残ります。

<想定される用途(高効率、低発熱、低出力リプルの三端子レギュレータ)>

・ 本技術には、小端子数ICに適用する事で端子数増加を抑えつつ、特性変更可能となる有用性

・ 上記以外に、品種管理を容易にする効果が得られることも期待

・ また、達成された速度と信頼性の両立に着目すると、小端子数の発振器、D/Aコンバータ、基準電圧発生器、各種センサなどの用途に展開することも可能

<実用化に向けた課題>

・ 現在、3端子レギュレータについて出力電圧設定が可能なところまで開発済み。しかし、簡単に扱える評価システム構築ができていない。

・ 今後、パソコン、マイコンなどから容易に1線シリアル信号パターンを設定し、信号発生できる装置の開発を行っていく。

<企業への期待>

・ 1線シリアルI/Fの普及、実用化、及び仕様の規格化については、意見集約や企業の協力により克服できると考えています。

・ IC設計の技術を持つ、企業との共同研究を希望します。

・ また、低コスト・高信頼性の電子機器を開発中の企業、電子デバイス分野への展開を考えている企業には、本技術の導入が有効と思われます。

・製造後性能補正が可能な3端子レギュレータを開発 ・特願2007-095928のアイデアの実証に成功 ・JSTからの海外出願支援を獲得、各国特許への移行を開始(2009.9~) * 2010 Asia and South Pacific Design Automation Conference (ASP-DAC)で発表予定 (2010/1/18)

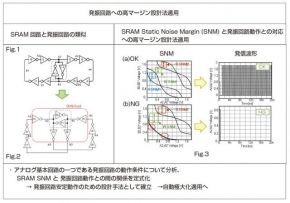

サブテーマ③

Static Noise Marginを用いた発信回路の高動作マージン設計法

本研究は、高速クロックデータリカバリ回路などに使われるCMOS偶数段リング発振回路の発振条件の解析方法とそれを用いた最適設計法に関するものです。

CMOSインバータチェーンからなるリング発振回路は、構造が非常に単純であり、高速・低電圧動作が可能なため、従来から広く用いられてきました。( Fig.1に、リング発振回路の動作原理図を示す)

私たちは、Fig.1のタイプの発振回路と、SRAMセルの類似性に着目することで、安定発振条件は、SRAMセル回路におけるRead/Write動作の Static Noise Margin解析と、基本的に等価であることを見出しました。Fig1の回路から、ラッチ回路と、その接点の前後のインバータ回路(I1-I4)、さらに、偶数段のインバータ部分を遅延線として抽出した回路をFig.2に示します。Fig.2の回路は、SRAMセルの構成に類似していることがわかります。ここで発振持続の条件は、SRAMセルへの書き込み/読み出しの安定動作を保証するためのStatic Noise Margin解析と等価であり、SRAMセルにおけるWrite Static Noise Margin(WSNM)>0でありかつ、Read Static Noise Margin>0であることに相当します。Fig.3に、この3つのマージンを同時にプロットしたSPICE によるDC解析(SNM特性)とTRANSIENT解析(発振波形)結果を示します。Fig3.(a)は、発振条件を全て満たすようにトランジスタサイズを設定した場合であり、Fig.3(b)は、1つの条件を満たさない(図の○印の箇所のマージンがない)ように設定した場合です。

図で、WSNM, RSNM1,RSNM2のマージン有無と、発振動作有無が対応している様子が確認できます。

Static Noise Margin (SNM) 指標を、発振回路の動作マージン解析に適用 ・ SNM と 発振回路動作との間の関係を定式化 → 発振回路安定動作のための設計手法として確立 (*1) → ラッチを複数個含む回路へ設計手法を拡張 (*2) *1 2008 International Conference on Solid State Devices and Materials (SSDM) で発表 (2008/9/25) *2 2009 International Conference on Solid State Devices and Materials (SSDM) で発表 (2009/10/8)